晶闸管功率控制和瞬态抑制用 RC 缓冲电路晶闸管在电压瞬态下保持阻断状态的能力

引言

RC 网络用于控制可能会误导通晶闸管的电压瞬态。这 类网络称为缓冲器。 简单缓冲器由串联电阻和围绕晶闸管放置的电容组成。 这些元器件与负载电感一同形成串联CRL 电路。缓冲 器理论的基础是电路的微分方程解。 许多 RC 组合都能提供可接受的性能。然而,若缓冲器 使用不当,则会造成电路工作不稳定,并损坏半导体器 件。 出于可靠性考虑,可能需同时采取导通和关断保护。有 时,晶闸管必须要能在某个负载范围内工作。使用的晶 闸管类型、电路配置和负载特性都有影响。 缓冲器设计时需要权衡取舍。这些权衡包括成本、额定 电压、峰值电压和导通应力。实际解决方案取决于器件 和电路的物理特性。

静态

什么是静态dV/dt?

静态 dV/dt衡量的是晶闸管在电压瞬态下保持阻断状态的能力。

(dV/dt)S 器件物理特性

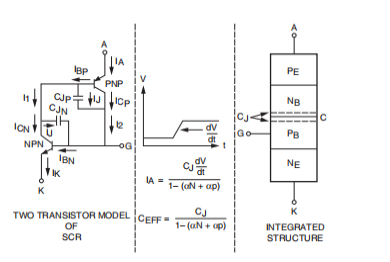

静态 dV/dt导通是米勒效应和重新生成的结果 (图 1)。 结点电容两端的电压变化含有电流流过该结点的效应。 该电流与电压变化率成比例![]() 。当其大至足以将 NPN 和 PNP 晶体管的α参数之和提升到 1 个单位时, 则触发器件。

。当其大至足以将 NPN 和 PNP 晶体管的α参数之和提升到 1 个单位时, 则触发器件。

图1 (dV/dt)S模型

影响条件(dV/dt)S

线路交叉或晶闸管两端无初始电压时发生瞬变是最差情 况。此时集电极结点电容最大,因为耗尽层在较高的电 压下会变宽。

较小的瞬变无法对栅极层的固有电容充电至其正向偏置 阈值电压 (图 2)。电容分压器位于集电极和栅极 - 阴 极结点之间,内置电阻从阴极 - 发射极分流,.造成该效应。

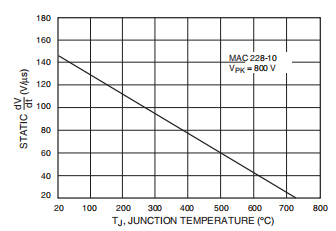

图2 (dV/dt)S指数与峰值电压的关系

静态dV/d在最大额定电压和额定温度以内工作时并不特 别依赖电压。如果瞬变大致在 50V 的实际器件击穿电压以内雪崩倍增将增加漏电流,同时降低能力。

额定电压较高的器件在较低电压下具有较高的保证dV/dt。 这是使用指数级额定法的结果,额定值为 50 V/µs 的 400 V 器件具有较高的dV/dt,为 200 V ;而相同额定值的 200 V 器件其值较低。但是同样的扩散方法通常适用于 所有电压。因此,产品的实际能力差别不大。

发热会增加电流增益和漏电流,降低dV/dt , 栅极触发电 压和抗噪能力 (图 3)。

图3. 指数(dV/dt)S与温度

(dV/dt)S 故障模式

瞬变导致的偶尔一次误导通在加热器电路是可以接受 的,但在防火喷淋系统或大型电机控制系统中不可以。 若后续的电流幅度或额定值过大,则导通具有破坏性。若晶闸管短接电源线或充电电容,则它将被损坏。

静态dV/dt当串联阻抗能够限制浪涌时,导通不具有破坏 性。晶闸管于半周期导通后关断。高dV/dt有助于电流在晶闸管内的流动,改善其耐受。击穿导通无此优点, 应避免。

改善(dV/dt)s

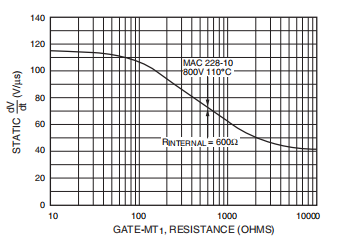

静态dV/dt可通过在栅极和 MT1 之间添加一个外部电阻加以改善(图 4)。电阻为漏电流提供路径,并且 ![]() 产 生的电流发源于驱动电路或晶闸管本身。

产 生的电流发源于驱动电路或晶闸管本身。

图 4.指数(dV/dt)S与栅极至 MT1 电阻的关系

非敏感器件(图 5)具有分散在芯片整块阴极区域的内 部短接电阻。这种设计特性改善抗噪能力和高温阻断稳 定性,但代价是增加触发和保持电流。外部电阻在非敏 感 SCR 和 TRIAC 中是可选器件。它们应当与器件内部 的短接电阻尺寸相当(20 至 100 Ω),以便最大程度改善性能。晶闸管的内部电阻应采用欧姆表,不会对二极管结点产生正向偏置。

TJ,JUNCTION TEMPERATURE (°C)

图 5.指数(dV/dt)S与结温

敏感的栅极TRIACS 具有100至1000Ω电阻。采用外部电阻,其dV/dt能力依然较非敏感器件为差,因为栅极层的横向电阻降低了它的优势。

敏感型栅极 SCR (IGT < 200 µA) 无内置电阻。它们必须 使用外部电阻。电阻推荐值为 1000 Ω。更高的电阻值会降低最大工作温度。dV/dt s(图 6)。根据栅极 - 阴极 端接,这些器件的能力从 100 到 1 不等。

图 6. 指数(dV/dt)S与栅极 - 阴极电阻的关系

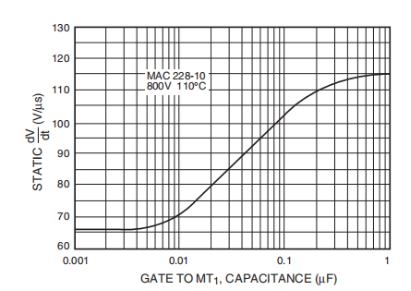

图 7. 指数(dV/dt)S与栅极至 MT1 电容的关系

栅极 - 阴极电容 (图 7)为瞬变电流提供分流路径,方式与电阻相同。它还会过滤来自驱动电路的噪声电流, 并增强内置栅极 - 阴极电容分压器的效果。栅极驱动电 路应能在无过多延迟的情况下对电容充电,但无需像对 电阻一样提供持续电流,以将dV/dt提高相同的量。然而,电容无法增强静态热稳定性。 最大dV/dt在短接时得以改善。

由于晶闸管内存在扩散电阻,真正的改善便止步于此。 使用数值约为 0.1 µF 的外部电容可获得更高 RGK 值的 最大性能增强。

应当保持晶闸管冷却,以获得最高的dV/dt 。另外,器件应当在应用电路中,以尽可能高的温度使用具有最低 测量触发电流的晶闸管进行测试。

什么是换向 dV/dt?

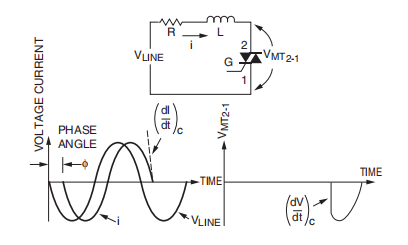

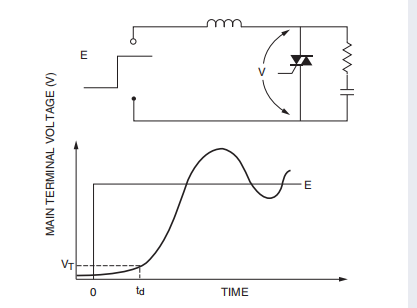

换向 dV/dt额定值在 TRIAC 导通并试图以感性负载关断时 适用。电流和电压不同相 (图 8)。当电流下降至维持值以下时, TRIAC 尝试关断。此时,线路电压较高,极 性与导通方向相反。成功的关断操作要求TRIAC 两端 电压以足够慢的速率上升至瞬时线路电压,以防再次触发器件。

图 8. TRIAC 感性负载关断(dV/dt)c

(dV/dt)c器件物理特性

一个 TRIAC 工作特性与两个反向并联连接的 SCR 类 似。因此,任意极性的瞬变均可导通该器件。

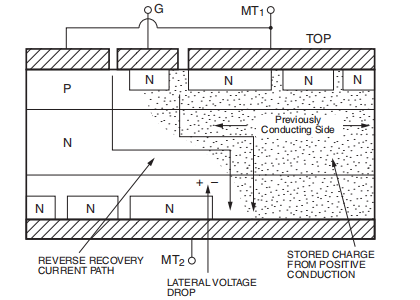

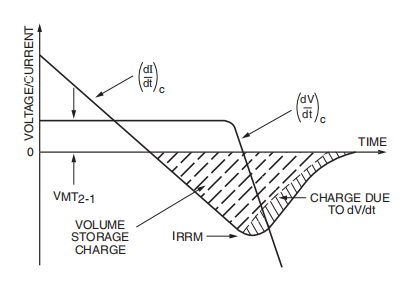

由于先前导通,晶振体内存在电荷(图 9)。集电极结 点耗尽层边界处的电荷会影响 (dV/dt)。TRIACS 具有更低的(dV/dt),相比(dV/dt)而言,因为存在该额外电荷。

图 9. TRIAC 结构和换向电流的流向

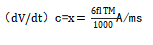

TRIAC 内存储的电荷量取决于关断前的峰值电流及其零交叉速率。(dV/dt)c 在经典电路中,负载阻抗和线路频率即可确定(dV/dt)c正弦波电流的零交叉速率由 50% 和 0% 电平之间的割线斜率给出:

其中, f = 线路频率, ITM = TRIAC 中的最大通态电流。 关断同时取决于米勒效应位移电流 (由dv/dt在集电极电 容两端产生)和器件内部存储的体电荷所产生的电流 (图 10)。如果来自这两部分的反向恢复电流都很大, 则 TRIAC 基层中的横向 IR 压降将正向偏置发射极,并 导通 TRIAC。顺着电流传导的正方向关断时,因为受器件几何形状的影响,换向dv/dt的能力较差。栅极位于芯 片顶部,阻碍电流流动。

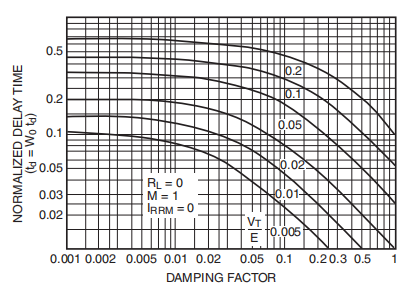

随着电流波形趋于零,在整个导通期间沿电流波形背面 进行重组。关断能力取决于其形状。如果电流幅度较小且零交(dl/dt)较低,则体电荷存储量较少,并且关断开始受限于(dl/dt)中等电流幅度时,体电荷开始影响关断特性,此时应使用较大的缓冲器。当电流较大,或者具有快速零交叉时,对(dl/dt)的影响很小。顺着电流传导的正方向关断时,因为受器件几何形状的影响,换向dl/dt和电压重加延迟时间决定关断是否成功。(图 11、 12)

图 10. 换向时的 TRIAC 电流和电压

图11.缓冲器延迟时间

图 12. 达到标准化电压的延迟时间

影响条件:(dv/dt)c

顺着电流传导的正方向关断时,因为受器件几何形状的 影响,换向dv/dt取决于电荷存储量和动态恢复时间,另 外变量也会影响静态dv/dt高温增加少数载流子的存活时间以及恢复电流的大小,使关断更为困难。减慢电流零交叉速率的负载有助于关断。带有谐波的内容会阻碍关断。

图 13. 桥式电路中控制电机的相位

电路示例

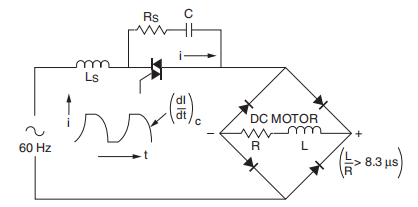

图 13 表示在桥式电路中使用 TRIAC 控制感性负载。感性负载的时间常数大于线路周期。这会使负载电流保持恒定,且TRIAC电流随线路电压的反向而快速开关。该应用由于会造成 TRIAC 关断困难而不受欢迎,因为 存在较高的 。 高电流导致高结温,电流零交叉速率也较高。电机在启动时的电流幅度可达正常工作电流的 5 到 6 倍。这同时增加了结温和电流零交叉速率,导致难以关断。 在 400 Hz 应用中,线路频率会造成电流零交叉速率过高。谐振变压器电路具有双倍周期,并且初级与次级谐振端都存在电流谐波。非正弦波电流会导致关断困难,即使零交叉之前电流幅度较低。

(dv/dt)c故障模式

(dv/dt)c故障导致失去相位控制。可能发生暂时性导通故障,或出现完全关断故障。如果 TRIAC 非对称导通,则该故障将是破坏性的,因为会导致直流成分以及磁饱和。线圈电阻可限制该电流。故是因为浪涌电流和结温过高。

改善(dv/dt)c

改善![]() s的步骤同样有助于改善 dv/dt,存储电荷主 导关断时除外。因此,有必要采取措施,减少存储电荷或软化换向电流。

s的步骤同样有助于改善 dv/dt,存储电荷主 导关断时除外。因此,有必要采取措施,减少存储电荷或软化换向电流。

给定负载的情况下,相比较小的 TRIACS,更大的 TRIACS 具有更佳的关断能力。较大 TRIACS 的电流密 度较低,允许重加电荷在内部电荷中占有更大的比例。 此外,结温也更低。

具有高栅极触发电流的 TRIACS 其关断能力较强,因为 栅极层的扩散电阻较低,从而降低米勒效应或者缩短载流子的存活时间。

通过增加一个换向软化电感,使其与负载串联,即可调 节电流零交叉速率。高磁导率 “方形环路”小电感饱和 使负载电流不存在严重干扰。电流过零后电感即复位, 导致此时缓冲器电路产生大电感。这会减慢电流零交叉速率,延迟阻断电压的重加,有助于关断。

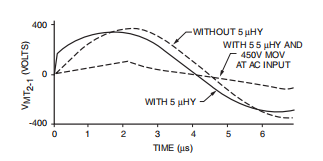

换向电感是电路的一部分,能使电路产生延时而非电感。它对器件所观察到的dv/dt几乎不产生影响。以下示例表明添加一个电感后得到的改善结果;电感由采用绕 带磁芯的 33 匝 18 号导线绕组构成 (52000 -1A)。该磁芯极小,其外径为 3/4 英寸而厚度为 1/8 英寸。

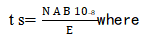

延迟时间可由下式计算得出:

ts = 达到饱和的时间延迟,单位为秒。

B = 饱和通量密度,单位为高斯。

A = 磁芯有效横截面积,单位为平方厘米。

N = 绕组匝数。

对于上述电感,有:

ts = (33 匝 )(0.076 平方厘米 )(28000 高斯 )(1 x 10-8)/(175 v) = 4.0 µs。

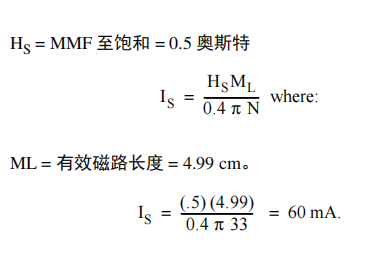

电感饱和电流无需比 TRIAC 触发电流高出很多。在恢 复电流高于该值以前,就会发生关断故障。这一条件使电感可通过下式进行调节:

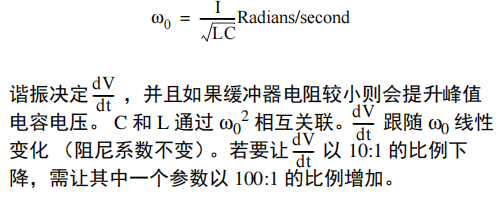

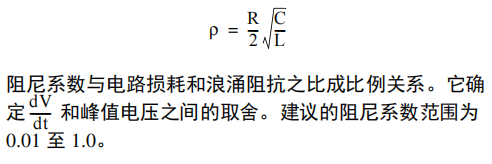

缓冲器物理特性

阻尼系数

缓冲器电阻

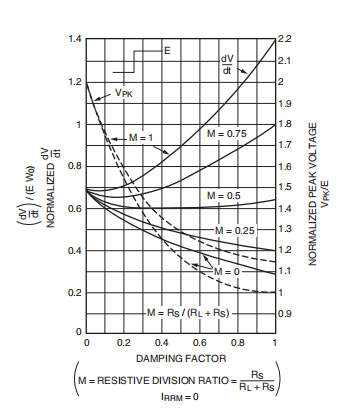

阻尼与dV/dt

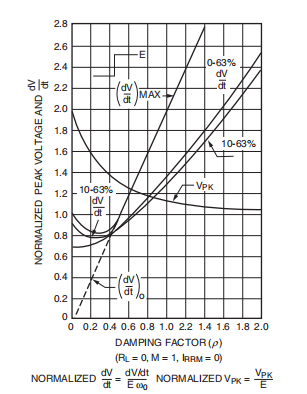

ρ < 0.5 时,缓冲器电阻较小,且dV/dt主要取决于谐 振。阻尼系数小于 0.3 时, dV/dt几乎没有改善,但峰值电压和缓冲器放电电流增加。电压波形为 1-COS(θ),并伴有过冲和振铃。最大值 ![]() 出现在 t = 0 以后。电压上升前存在时间延迟,峰值电压几乎翻倍。

出现在 t = 0 以后。电压上升前存在时间延迟,峰值电压几乎翻倍。

当 ρ > 0.5 时,电压波形几乎呈指数变化。最大瞬时dV/dt出现在 t = 0时刻。几乎没有时间延迟,并存在中等程度的电压过冲。

当 ρ > 1.0 时,缓冲器电阻较大,且dV/dt主要取决于其数 值。电路存在一定程度的过冲,哪怕此时处于过阻尼状态。

高负载电感要求大缓冲器电阻和小缓冲器电容。低电感要求小电阻和大电容。

阻尼与瞬变电压

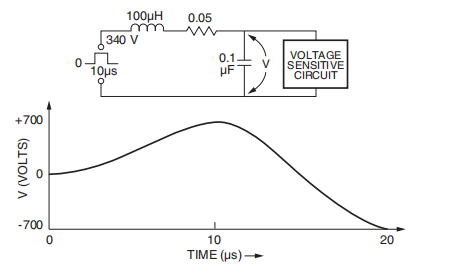

图 14 显示串联电感和滤波器电容连接在交流市电线路 两端。瞬变干扰中的峰峰值电压上升幅度几乎达到了 4 倍。另外由于振铃,导致干扰持续时间延长,增加了电压敏感型电路出现故障或损坏的风险。关断开关会造成 这一现象。添加一个阻尼电阻使其与电容串联,可缓解该问题。

图14. 无阻尼 LC 滤波器放大并延长瞬变

非感性电阻

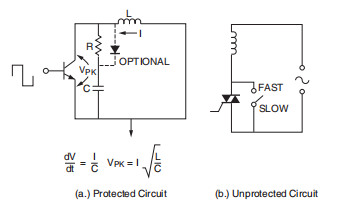

缓冲器电阻可限制电容的放电电流,并减少 dl/dt应力。高dl/dt会损坏晶闸管,哪怕脉冲持续时间非常短。电流上升 速率直接与电路电压成正比,与串联电感成反比。缓冲 器通常是损坏晶闸管的主要原因,因为它具有低电感, 且位置靠近晶闸管。

若没有瞬态抑制器,电容两端的最大电压值就是晶闸管的击穿电压。它可能超过多个器件的最高额定电压值,因为高压器件经常用于为低电压规格供电。

缓冲器电阻最小值取决于晶闸管类型、触发象限、栅极 电流幅度、电压、重复或非重复操作和所需预期寿命。电流上升速率无法简单预测,因为它取决于晶闸管的导 通速度、电路布局、缓冲器电容的类型和大小,以及缓冲器电阻中的电感值。附录 D 中的等式描述了该电路。然而,模型所需的数值除通过测试外,无法轻易获取,因此,应在实际应用电路中验证可靠性。

表 1 显示建议的最小电阻值;这些数值通过测试四种不同 TRIAC 芯片尺寸的 20 个样片来估算。

表1. 四象限触发的最小非感性缓冲器电阻。

|

TRIAC 类型

|

峰值 VC 电压

|

RS ( Ω )

|

dl dt A/µS

|

|

非敏感栅极 (IGT > 10mA) 8 至 40 A(RMS)

|

200 300 400 600 800

|

3.3 6.8 11 39 51

|

170 250 308 400 400

|

降低dl/dt

TRIACdl/dt可通过避免四象限触发而加以改善。大部分光电耦合器电路在第一和第三象限操作 TRIAC。集成电路驱动器则使用象限二和象限三。零交叉触发器件很有用,因为它们可在电压过高时禁止触发。

以高幅度快速上升的脉冲驱动栅极可提高能力。栅极额定值部分定义允许的最大电流。

与缓冲器电容串联的电感可降低 dl/dt。防止缓冲器dV/dt抑制能力下降的电感值不应超过负载电感的 5%。绕线缓冲器电阻有时可实现这一目标。或者,可使用一个独立的电感,与缓冲器电容串联连接。该独立电感可以取较小值,因为它不需要搭载负载电流。例如,采用 T50-3(1/2 英寸)铁粉磁芯的 18 匝 AWG 20 号导线即可形成 一个 6.0 µH非饱和电感。

10 Ω、 0.33 µF 缓冲器充电至 650 V,可获得 1000 A/µs 以 dl/dt 20 W 绕线单元替换非感性缓冲器电阻可将上升速率降低至不具有破坏性的 170 A/µs (800 V)。使用非感性电阻,电感在 800 V 时具有 80 A/µs 的上升速率。

缓冲器电容

0.3 的阻尼系数可最大程度降低缓冲器电容值 (给定的dl/dt。它可降低成本和电容的物理尺寸。然而,它会升 高电压,增加平衡成本。

缓冲器操作依赖于缓冲器电容的充电。关断缓冲器要求最小导通角度足够长,以便对电容放电。它至少应是 (RS CS) 常数的数倍。

存储电能

感性开关瞬变

E =1/2 L IO 2 Watt-seconds or Joules

IO = 流过电感并以安培表示的电流 (t = 0)。

关断时,谐振充电无法对电源增压至 2 倍以上。如果关 断时负载电感内有初始电流流过,则有可能可以获得高 得多的电压。TRIAC 关断时可忽略电能存储,因为它具 有低维持或恢复电流。

额外的开关(如继电器、恒温器或断路器)允许在开关打开时打断负载电流并产生高尖峰电压。电感内的电能转换为电路电容,并确定峰值电压(图 15)。

图 15. 中断感性负载电流

电容放电

存储在缓冲器电容中的电能在每次导通时传送至缓冲器电阻和晶闸管。功耗与频率成正比(PAV = 120 EC @ 60 HZ)。

电流引导

负载电感内流过的电流无法即刻改变。该电流导入缓冲器电阻,理论上导致无穷大的dl/dt 尖峰,幅度等于(IRRMR) 或 (IHR)。

负载相位角度

高度感性负载导致关断时电压和dl/dt上升。然而,它们有助于保护晶闸管免受瞬变影响,以及 dl/dt若器件确实导通,则负载可用作缓冲器电感,限制涌入电流的速率。负载电阻降低dl/dt和 VPK(图 16)。

图 16. 0 至 63% DV/dt

电压波形特性

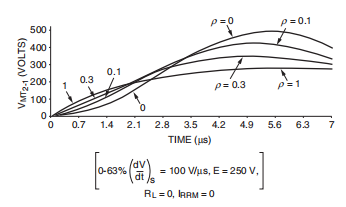

阻尼系数和反相恢复电流确定电压波形。缓冲器阻尼系数低于 0.5 或存在极高恢复电流时,波形不呈指数变化(图 17)。

图 17. 不同阻尼系数下的电压波形

图18. 权衡取舍:VPK 与dv/dt

各种波形参数(图 18)可描述dv/dt某些参数容易求解,而且有助理解。这些参数包括:初始 、最大瞬时dv/dt以及到达峰值重加电压的平均dv/dt 。0 至 63% dv/dt以及 10 至 63%dv/dt 的定义参见器件数据手册,它们很容易测得,但难以计算。

非理想特性

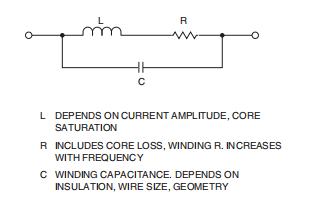

磁芯损耗

在缓冲器的自然频率下,典型 60 Hz 负载的磁芯材料会 产生损耗。它们表现为负载电感和绕组直流电阻的串联电阻(图 19)。这使得实际的dv/dt低于理论值。

图19. 电感模型

复杂负载

现实中,很多电感都是非线性的。它们的磁芯材料不是有隙的,这导致电感随电流幅度而改变。很难通过小信号测量对它们进行特性化。出于建模的需要,最好的方法是在实际应用中对它们进行测量。

应检查复杂负载电路在导通和关断时的瞬变电压和电流。使用容性负载,在峰值输入电压下导通时会产生最大浪涌电流。电机起始电流比稳态值要高 4 至 6 倍。发生器可将电压提升至线路值之上。白炽灯的冷启动电流比稳态值高 10 至 20 倍。变压器通电时产生电压尖峰功率因数校正电路和开关器件会产生复杂的负载。大部分情况下,简单CRL 模型允许对缓冲器进行近似设计。然而,测试与测量最差情况的负载条件却是无可取代

的。

感性电路中的浪涌电流

启动时,具有较长 L/R 时间常数的感性负载会产生非对称多周期浪涌 (图 20)。电压过零点触发是最差情况。可利用电流过零点触发抑制浪涌。

图 20. 感性电路的启动浪涌

磁芯的剩余磁通量和饱和会引起浪涌电流。浪涌电流大小取决于触发角度、线路阻抗、磁芯特性和残余磁化方向。例如, 2.8 kVA 120 V 1:1 变压器在 1.0 A 负载下会产生 160 A 的启动电流。以较小的导通角度软启动电路可减少浪涌电流。

变压器磁芯一般都不是有隙的,因此很容易饱和。导通角度的微小非对称性就会导致磁饱和以及多周期电流浪涌。

获得可靠操作的步骤包括:

提供足够的触发电流幅度。 TRIAC 的触发电流各不相同,具体取决于它们的工作象限。临界栅极电流或光电耦合器 LED 电流导致半波工作。

2. 提供足够的栅极电流持续时间,以便达到闩锁要求。感性负载减慢主端电流的上升速度。栅极电流必须保持在 IGT 额定值以上,直到主端电流超过闩锁值。负载和缓冲器附近的两个泄放电阻可放电,有助于闩锁。

3. 使用缓冲器防止 TRIAC 故障。

4. 尽量减少设计导入的触发器非对称性。每半个周期都必须正确触发,包括第一个周期。使用存储示波器查看导通中前几个周期的电路特性。或者,对负载通电前启动栅极电路。

5. 从线路 (而非 TRIAC 主端电压)获取触发器同步信号。这可避免磁芯滞后和触发角度之间的再生交互,防止触发失控、半波操作和磁芯饱和。

6. 启动时避免高浪涌电流。使用电流探针确定浪涌幅度。使用软启动电路降低浪涌电流。

分布式绕组电容

线圈的圈与层之间存在小电容。这些小电容汇总后,可视为单个分流电容。在频率高于它自谐振频率时,负载电感变现的像电容。当发生快速瞬变时 (比如开关关断时产生的瞬变),控制和 VPK 就会变得低效率。通过在线路上增加一个小型缓冲器即可解决该问题。

自电容

晶闸管具有自电容,当负载电感较大时会限制 。大负载电感、高功率因数和低电压可允许无缓冲器工作。

缓冲器示例

无电感

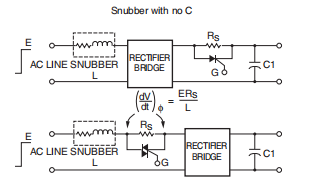

功率 TRIAC 示例

图 21 显示瞬变电压施加于 TRIAC,控制阻性负载。理论上,TRIAC 两端将会立即产生一个阶跃电压。减慢该速率的两个因素是绕组的电感和晶闸管的自电容。由于缓冲器电阻中存在 IR 压降,因此加入了一个指数电容充电元器件以及衰减元器件。当负载电阻远高于缓冲器电阻时,非感性缓冲器电路非常有用。

图 21. 非感性缓冲器电路

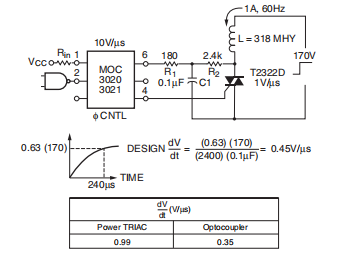

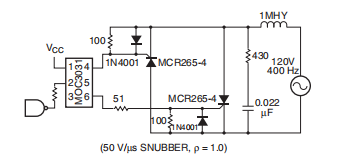

光电 TRIAC 示例

单缓冲器,时间不变设计

图 22 表示采用 RC 时间常数的设计方法。对于光电耦合器而言,仅存在通过缓冲器电容的电压。电阻 R1 提供功率 TRIAC 的触发电流。针对最差情况的设计假定功率 TRIAC 的电压瞬时改变。电容电压在一个时间常数的时间内上升至最大值的 63%。

图 22. 用于敏感型栅极 TRIAC 和相位可控型光电耦合器的单缓冲器 (ρ = 0.67)

光电耦合器导通电流的时间仅够触发功率器件。导通时, MT2 和栅极之间的电压会下降至光电 TRIAC 正向 阈值电压以下,导致关断。当功率 TRIAC 在稍后的零电流交叉导通周期中关断时,对于光电耦合器而言,只dv/dt存在。因此,无需针对更低的光电耦合器dv/dt额定值进行设计。本例中,针对光电耦合器设计的单个缓冲器即可同时保护两个器件。

图 23. 反并联 SCR 驱动器

SCR 的光电耦合器

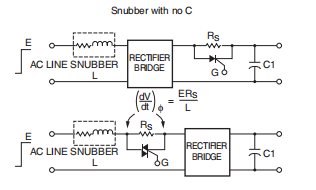

反并联 SCR 电路在光电耦合器和 SCR 上分别具有相同的 dv/dt(图 23)。相位可控型光电耦合器要求 SCR 缓冲至较低的dv/dt额定值进行设计。反并联 SCR 电路无电荷存储特性——该特性会降低 TRIAC 的关断能力。所 有 SCR 都导通半周期,下半个周期用于交流线路恢复。 传导 SCR 的关断dv/dt对其他器件而言变为静态正向阻断dv/dt。在缓冲器设计中使用 SCR 数据手册中dv/dt的额定值。

整流电桥内的 SCR 用于控制交流负载;该 SCR 将无用于恢复的半周期。可用时间随线路电压的上升而减少。这使得该电路不那么好用了。可利用输入至电桥或横跨SCR 的缓冲器抑制感性瞬变。但是,时间限制依然适用。

光电dv/dt c

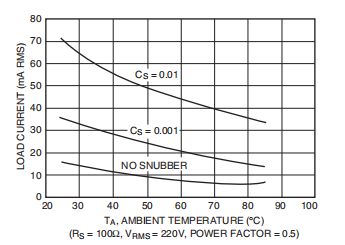

电流低于 100 mA 时,可使用过零光电耦合器来开关感性负载 (图 24)。然而,若要获得更高的负载电流,可将功率 TRIAC 搭配光电耦合器使用。

图 24. MOC3062 感性负载电流与 TA 的关系

配合功率器件时,建议使用相位可控型光电耦合器。当负载电流较小时,适合使用 MAC97 TRIAC。

异常电路条件有时会导致光电耦合器在dv/dt模式中的误操作。功率器件中极高的电流导致 MT2 和栅极之间的电压上升,并使栅极保持光电耦合器导通状态。使用较大的 TRIAC 或采取其他手段限制浪涌电流即可解决这一问题。

极短的导通时间使光电耦合器中存在残留电荷。微小的导通角度允许在电压重加前进行恢复。

带电感的缓冲器

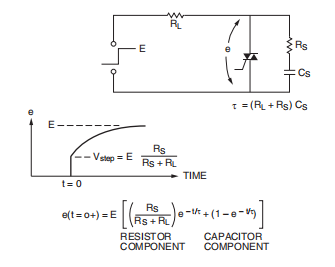

考虑一个使用大电容的过阻尼缓冲器,其电容电压在考察期间变化不大,则电路简化为等效 L/R 串联充电电路。

高度过阻尼缓冲器电路是不实用的设计。该例说明几个问题:

1. 初始电压看似完全施加在电路电感上。因此,它决定了流过缓冲器电阻的电流变化速率,以及初始dv/dt 。当负载中存在电阻时,该结果不变,并对所有阻尼系数都为真。

2. 缓冲器能够起到作用,因为电感控制通过电阻的电流变化速率和电容充电速率。缓冲器设计无法绕过电感。这种方法暗示,缓冲器电容无关紧要,但仅在这种假设性条件下适用。不存在电容时,缓冲器电阻分流晶闸管,造成无法接受的漏电流。若功率损耗是可以接受的,则dv/dt可以不通过电容直接控

制。一个示例是软启动电路,用于限制开关电源中的浪涌电流 (图 25)。

25. 开关电源中的浪涌电流限制

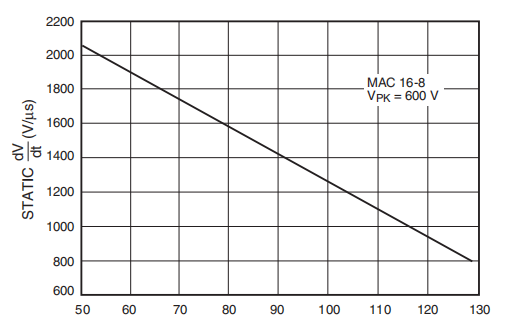

(dV/dt)c安全区域曲线

图26 显示 MAC16 TRIAC 的关断安全工作区域曲线。在该曲线下方进行关断则不会有任何问题。该区域以静态dV/dt在低数值(dl/dt)以及高电流时的延迟时间为边界。

减少峰值电流可允许电路工作在更高的线路频率下。该TRIAC 工作在 f = 400 Hz、 TJ = 125 °C 和 ITM = 6.0 A下,使用 30 Ω和 0.068 µF 缓冲器。低阻尼系数可扩展器件的工作范围至更高的(dl/dt),但电容大小会增加。加入小数值可饱和换向电感将引入恢复延迟时间,扩展允许的额定电流值。

图 26.(dV/dt)c 与(dl/dt)c TJ = 125 °C

静态dV/dt设计

通常在交流市电和电源绕组中存在一定量的电感。如果电路中有变压器的话,则电感可能大于 100 µH ;如果存在分流功率因数校正电容的话则电感接近零。一般线路电感约为数 µH。最小电感值必须是已知的,或通过增加一个串联电感加以定义,以确保可靠性 (图 27)。开始设计时建议使用 100 µH。将假定的电感值代入等式中的 C。更大的电感值会使缓冲器电阻更高,并降低dl/dt。

图 27. 缓冲阻性负载

可变负载

缓冲器应当设计为具有最小的负载电感,因为将由于对 ω0 的依赖关系而达到最高值。这就需要使用电压更高的器件在最大电感情况下工作,因为相应的阻尼系数较低。图 28 描述了各种功率因数下用于 8.0 A 负载的。最小电感是为了防止阻性负载静态点火而增加的元器件

图 28. 可变负载的缓冲器

缓冲器设计示例

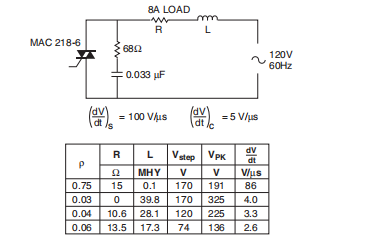

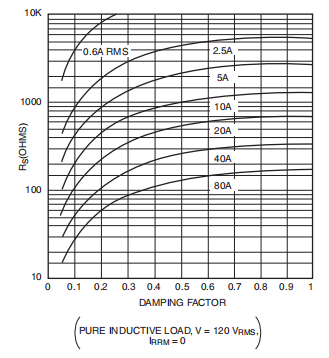

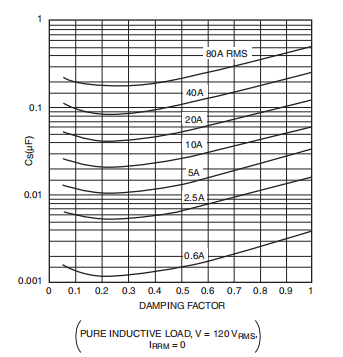

表 2 描述了缓冲器的 RC 值,用于dv/dt图 31 和 32 显示可能的 R 和 C 值,用于dv/dt 5.0 V/µs ,假定纯感性负载.

表 2. 静态dv/dt设计

(E = 340 V, Vpeak = 500 V, ρ = 0.3)

|

|

5.0V/µs

|

50V/µs

|

100V/µs

|

|

L µH |

C R µ FR

|

C R µF Ω

|

C R µF Ω

|

|

47 100 220 500 100 0 |

3.0 11

|

0.33 10 0.15 22 0.03 51 8 0.03 100 3 |

0.15 10 0.1 20 0.03 47 3 0.01 110 5 |

瞬变与噪声抑制

瞬变可通过正常的电路工作从内部发生,或由外部环境引起。后一种情况特别令人烦恼,因为瞬变特性未定义。可应用静态描述。更高或更低的应力都有可能。相比持续时间长、电压高的瞬变,更有可能发生幅度更小、频率更高的瞬变。环境中不常发生的照明和负载切换会造成 3.0 kV 以下的瞬变电压。

图 29. 缓冲器电阻,用于(dv/dt)c= 5.0 V/µs

图 30. 缓冲器电容,用于(dv/dt)c= 5.0 V/µs

室内交流线路的自然频率和阻抗产生典型频率范围为30 kHz 至 1.5 MHz 的阻尼振荡浪涌。浪涌幅度取决于线路和浪涌能量源。在远离源端的地方则几乎不会造成任何干扰。不存在瞬变抑制器时,以火花放电电压(室内交流线路上 6.0 kV)作为最大电压值。靠近进线口或重型布线中的瞬变具有较高的幅度、较长的持续时间和更多阻尼,因为这些位置电感较低。

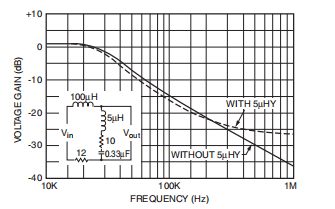

简单的 CRL 缓冲器是一个低通滤波器,可衰减高于其自然谐振的频率。稳态正弦波输入电压能够以同样的频率产生正弦波输出。无缓冲器电阻的情况下,下降速率接近每倍频程 12 dB。转角频率为衰减器的自然谐振频率。若阻尼系数较低,则峰值响应频率即为该频率。缓冲器电阻降低滤波器特性,在 ω = 1/(RC) 处产生一个向上的趋势。在频率高于此数值时,下降接近每倍频程6.0 dB。缓冲器电阻中的电感进一步降低了下降速率。

图 32 描述了图 27 中电路的频率响应。图 31 给出3.0 kV 100 kHz 振铃波的理论响应。缓冲器降低晶闸管上的峰值电压。然而,将电感与缓冲器电阻串联时,快速上升的输入导致高dv/dt阶跃。利用瞬变抑制器限制输入电压可减少此阶跃。

图31. 电路对 3.0 kV IEEE 587振铃波的理论响应 (RSC = 27.5 Ω)

图 32. 缓冲器频率响应(Vout/Vin)

若通过杂散电容进行耦合,则电路内的感应噪声与dV/dt成比例;若通过互感进行耦合,则感应噪声与dV/dt成比例。若要获得最好的抑制效果,则需使用限压器件以及限额 CRL 缓冲器。通过防止dV/dt

导通或击穿,晶闸管得到了良好的保护。应针对可能发生的情况设计电路,而非一般情况。

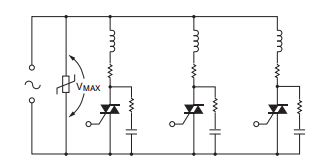

图 30 中,线路上的 MOV 保护大量并联电路分支及其负载。 MOV 定义最大输入电压以及负载上的dV/dt。通过缓冲器,它便可确定晶闸管上的最大dV/dt和峰值电压。MOV 必须足够大,因为电路中几乎无浪涌限制阻抗可防止器件烧毁。

图33. 限制线路电压

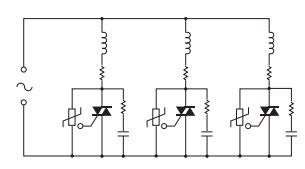

图 32 中,每个晶闸管两端都有一个独立的抑制器。负载阻抗限制来自线路的浪涌电能。它允许使用额定值较小的器件,但无负载保护。当晶闸管的负载是潜在的瞬变源时,这种配置能够保护每一个晶闸管。

图 34. 限制晶闸管电压

有必要将抑制器件直接放置在瞬变电能的源端,以防电能通过感应进入其它电路中。然而,针对负载与其控制晶闸管之间的电能注入却不存在任何保护。将抑制器直接放置在每个晶闸管两端可主动限制最大电压和缓冲器放电dl/dt

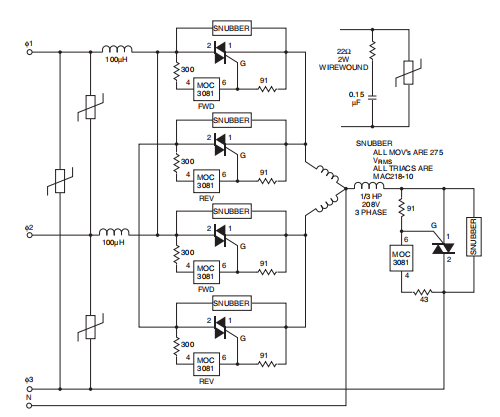

图 35 中, TRIAC 开关一个三相电机,并使其反向旋转。每对 TRIAC 都用作 SPDT 开关。 TRIAC 的导通动作会将线路相位之间的差分电压施加到阻断器件上,却不会带来电机阻抗限制电压上升速率的好处。加入电感,防止静态dV/dt引燃和线路间短路。

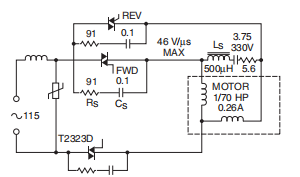

图 36 显示通过开关与其中一个绕组串联的电容,可实现裂相电容的反向驱动电机。正向和反向 TRIAC 用作SPDT 开关。反向旋转电机可将电容上的电压急剧施加到阻断晶闸管。此处再次添加电感 L,防止dV/dt引燃阻断 TRIAC。若发生导通,正向和反向 TRIAC 使电容 (CS) 短路并造成损坏。明智的做法是加入电阻 RS 限制放电电流。

图 35. 三相反向电机

图 36. 裂相反向电机

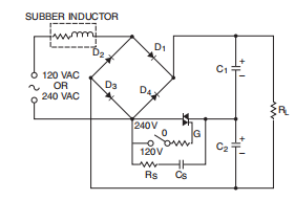

图37 是一个 “抽头转换器”。该电路允许开关 120 或240 vac 线路电压的电源。TRIAC导通时,该电路用作传统倍压器, D1 和 D2 交替导通半周期。在这种工作模式下,浪涌电流和dl/dt对 TRIAC 的可靠性产生不利影响。有必要使用串联阻抗防止损坏 TRIAC。

电路未倍压时, TRIAC 关断。在关断状态下,对TRIAC 而言,线路与 Cl 和 C2 交点处具有不同的电压值。线路瞬变导致dV/dt引燃TRIAC。高浪涌电流、和过压可能损坏滤波器电容。为了保护器件,要求在TRIAC 两端添加一个 RC 缓冲器,并在线路上串联一个电感。

图37. 用于双路电压开关的抽头转换器

晶闸管类型

敏感的栅极晶闸管很容易导通,因为它们的触发电流要求较低。但是,相对类似的非敏感器件,它们的dV/dt能力较差。应使用非敏感晶闸管,以获得较高的dV/dt。TRIAC换向dV/dt额定值相比静态时的额定值低5至20倍。dV/dt额定值。

相位可控型光电耦合器相比过零光电耦合器和功率TRIAC具有更低的dV/dt额定值。如果存在直流电压元器件,或者要防止导通延迟,则需使用这些器件。过零光电耦合器相比功率晶闸管具有更高的

dV/dt能力;并且在静态开关应用中,它们应代替相位可控型器件使用.

图38. 缓冲器放电dl/dt测试

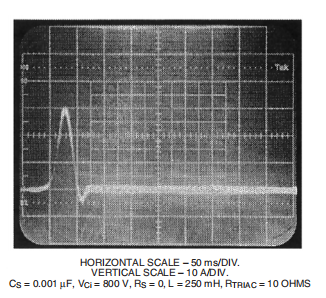

图39.0.001 µF 电容的放电电流

测量 (dV/dt)s

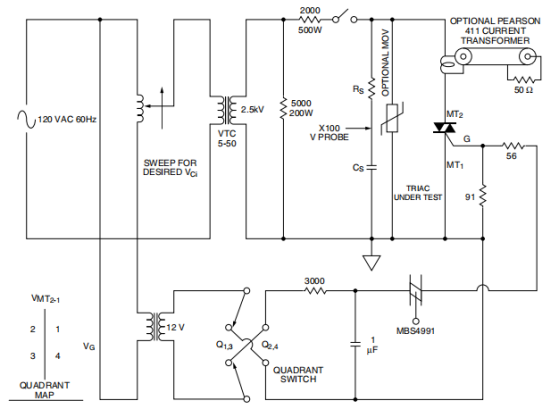

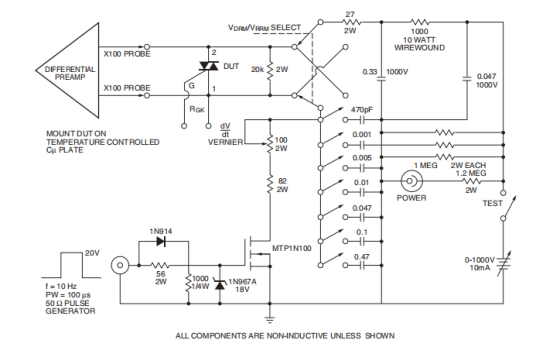

图 40 显示测量功率晶闸管静态dV/dt的测试电路。1000 VFET 开关确保待测器件 (D.U.T.) 两端的电压从零快速上升。差分前置放大器允许使用 N 沟道器件,同时出于安全起见,保持存储示波器外壳接地。电压上升的速率可通过可变 RC 时间常数进行调节。充电电阻较低,以防晶闸管自电容导致的波形失真,但又足够大,可防止导通损坏 D.U.T。dl/dt。将微型范围开关、电容和G-K 网络靠近待测器件安装可减少杂散电感,允许以高于10 kV/µs 进行测试。

图 40. 功率晶闸管的静态dV/dt测量电路

测量 (dV/dt)c

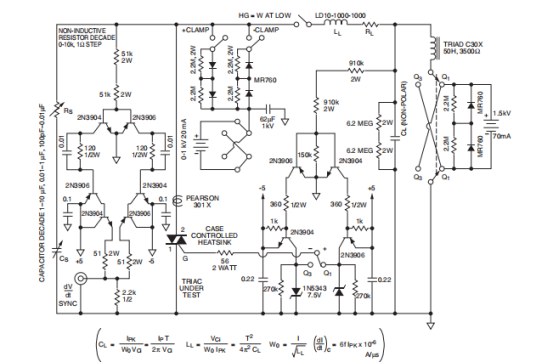

测量换向dV/dt的测试夹具如图 41 所示它是一个电容放电电路,带有串联负载谐振。单脉冲测试有助于温度控制,并允许使用功率更低的元器件。负载电容中的限制电能降低烧伤与触电危险。传统负载和缓冲器电路提供恢复和阻尼性能,与在应用中相同。

负载电容上的电压触发 D.U.T。当负载电容电压过零且TRIAC 电流达到峰值时,它可端接栅极电源。

每种 VDRM、 ITM 组合都需要不同的元器件。利用图 41中的等式计算它们的数值。

商用扼流圈简化所需电感的构建。应当通过增加磁芯中的气隙调节电感值。移除磁级片可降低 4 到 6 的电感,但会扩展不饱和电流。

负载电容由一组平行的 1500 V 直流非极性单元组成,单个泄放电阻搭配单个电容安装,保证安全性。

可选的可调节电压钳位防止 TRIAC 击穿。

若要测量dV/dt,将存储示波器与电流波形同步,并验证正确的电流幅度和周期。必要的话,可以增加电容上的初始电压以补偿线圈中的损耗。调节缓冲器,直到第一个半周期后器件无法关断。在最快通流条件下检查电压上升的速率。

图 41. (dV/dt)c 测试电路,用于功率TRIAC